Networked SSD: Flash Memory Interconnection Network for High-Bandwidth SSD

作者:Jiho Kim, Seokwon Kang, Yongjun Park, John Kim

@ KAIST(Korea)

相比于以往flash存储总线中专用信号通信的机制,本工作利用packetized通信机制来扩展flash memory的带宽;提出了适用于flash memory的互连网络拓扑,提升了数据转移路径的多样性;在此基础上,设计了最小化IO干扰的GC机制。

论文为什么要做这件事?

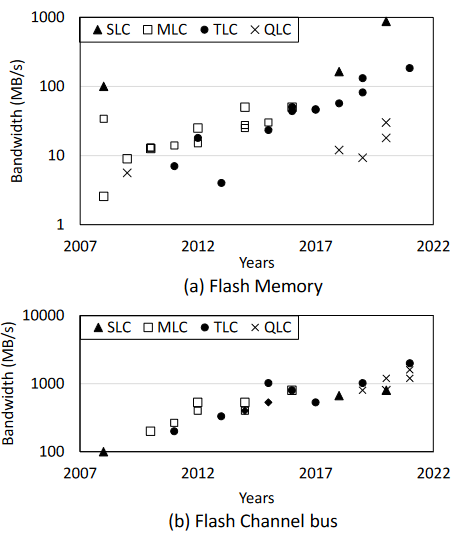

图 过去15年Flash memory的写带宽以及flash channel总线带宽发展趋势

- 趋势+Flash channel与flash memory一对多,使得flash channel总线上的带宽成为系统瓶颈

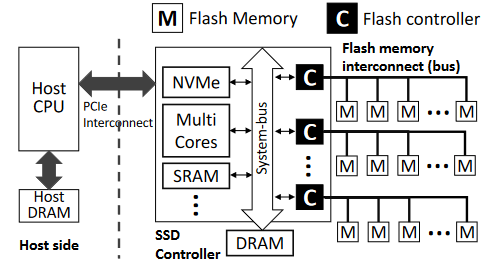

图 SSD内部结构

- 现有方案的限制:flash channel使用多种专用信号进行控制,这导致了很低的带宽利用率。

例:NV-DDR4接口中,10/18个引脚被用来数据传输,其他的引脚为专用控制接口,不能用来数据通信

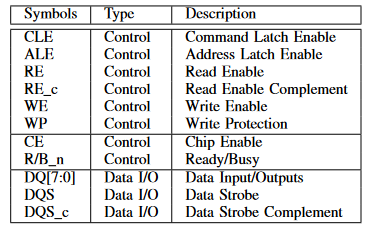

图 在Open NAND Flash Interface(ONFi)中的Flash接口信号描述(10/18)

替代方案:将控制信号的信息融入报文(packet),使用packet在SSD控制器和flash memory之间通信,尽可能多的利用现有物理信道所能提供的带宽,起到扩大flash channel带宽的作用。事实上,通过提升硬件频率或者增加新的信道引脚也能提升性能,但是这些方案受到功率或物理引脚的限制。

packet通信的另一好处:支持flash之间的互连。当实现flash之间的互连后:

可以将SSD的内部通信(指flash之间的通信,例如GC)和外部的通信(指flash与host的通信,例如IO)分离开

可以提供数据转移路径的多样性,以实现不同数据channel之间的负载均衡。当信道带宽如果是系统的瓶颈时,负载均衡带来的影响将更加严重。

图 8C8W-SSD系统中读写操作时信道的负载均衡表现。写均衡,读不均衡

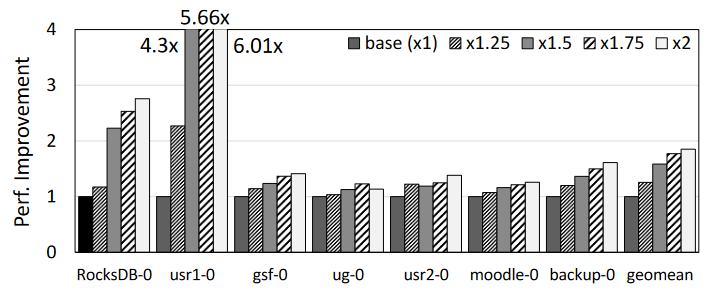

当信道带宽提升2倍时,在下面8个应用中,性能预期能够平均提升85%。(减轻了负载不平衡的负担)在个别非常不均衡的应用上,性能能提升6倍。

图 不同workload下,当提升带宽时,模拟应用的性能表现。最高模拟到信道带宽提升2倍

这个事情之前别人是怎么做的,存在什么问题?

- **互连网络(Interconnection Network)**:提出了大量网络拓扑结构。包括直接拓扑、间接拓扑、NoC拓扑等。Network-on-SSD也是第一个提出替代传统的flash memory总线的SSD内部网络的方案。核心区别是:本文认为多跳网络在SSD中并不实用。之前也没有利用多维总线拓扑来实现SSD内部flash的互联系统的方案。

- 基于packet的(packet-based communication)通信:基于packet的接口在NoC、memory-semantic fabric(GenZ, CXL)等实现处理器、加速器、内存之间互连的方案中都有涉及。但是由于协议开销,它们不一定适用于SSD内的内部芯片间通信。此外,SSD中芯片到芯片的接口限制带来了独特的挑战,包括有限的引脚接口、对硬件路由器或交换机的有限支持等。

该论文解决了什么难点,难点存在的原因是什么,作者是如何发现这些难点的?

难点1:最小化额外开销

packetized通信的额外开销需要最小化。

例如,在flash中使用带有缓冲区的传统路由器或交换机是不可行的。

难点2:网络拓扑设计

虽然packetized接口为实现flash之间互连的网络打下了基础,但由于flash的引脚带宽有限,先前提出的网络拓扑不适用。

难点3:Flash之间信道如何利用?

当前的系统对新型的网络拓扑无法利用。本文提出了新的GC机制,说明了如何利用这种连通性,通过分离I/O和GC来显著降低尾延迟。

针对以上难点,作者各做了哪些优化,优化背后的思想是什么?

本工作主要贡献点包含三个方面:

- 用packetization的思想拓宽了信道的带宽,实现了packetized SSD

- 建立在packet之上,设计了flash之间互连的网络拓扑

- 应用新的网络拓扑实现了一种新的垃圾回收机制

Pakectized SSD架构

基于packet的Flash互连

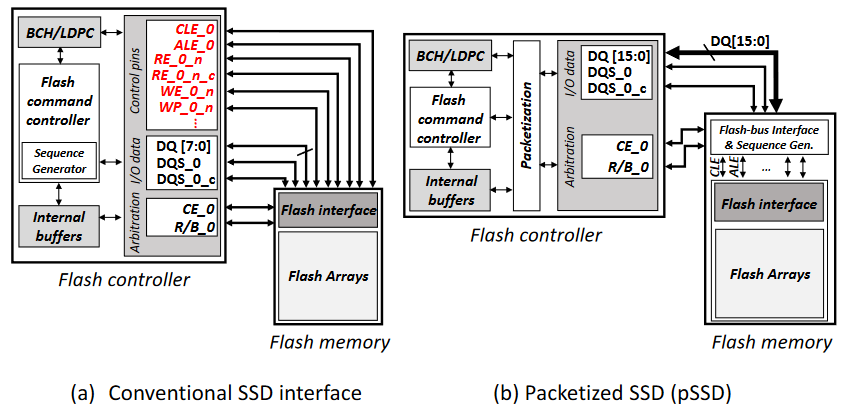

图 方框图的接口(a) 基于信号的传统SSD机制 (b) 基于packet的接口,修改了控制器和flash存储

- 两个保留的控制信号:CE和R/B,实现Flash控制器和Flash memory之间的握手通信机制,以决定哪个flash memory能够访问信道。其他的控制信号全部被打包进packet。数据通道引脚(DQ)因此而扩展了一倍,从8位变到了16位。

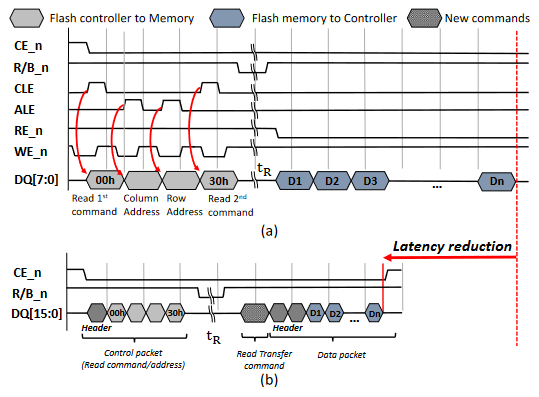

图 读事务的时序图。(a)基于信号接口的传统**SSD (b) 基于packet接口的SSD

- 时序图分析:基于packet接口的SSD由两种信息类型,一种是控制packet,另一种是数据packet。控制packet负责必要的命令和地址,数据packe包含带有数据头的页数据。不同点:(a)用RE_n信号指示数据读取,(b)增加了一条新的指令Read data transfer来指示数据读取。

微架构

- Flash信道控制器的微架构

- 握手机制:通过CE和R/B信号实现

- 其他改动:将原来在Flash控制器中的时序生成器移动到flash memory内部,flash控制器负责生成带有数据头的packet,数据头用来表示这个packet的类别是数据或控制包。

- 这样做提供了两倍的flash channel带宽。

- Flash memory的接口

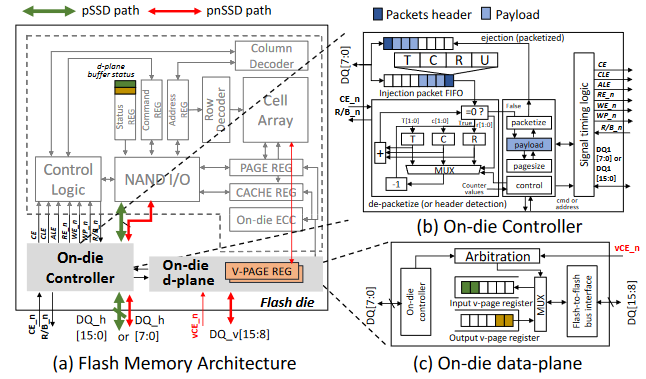

图 (a)flash memory架构的接口图 (b) die上的控制器 (c) die上的数据平面

- 不变的部分:虽然flash controller和flash memory之间的接口被修改了,但由于在外部引脚和内部flash die之间引入了控制器逻辑,因此内部的flash和组织未进行修改。

- on-die controller:负责解译packet头,为底层的flash memory生成相应的控制信号信息。其输入为DQ和握手信号,实现方面主要是使用状态机生成合适的控制信号。

- On-die data plane:包含一个额外的buffer,我们叫做V-page寄存器组。在后面的flash间通信会用到这个模块,它可以提供flash之间通信的路径。如果仅仅是想扩大带宽,这一部件也可以不用。

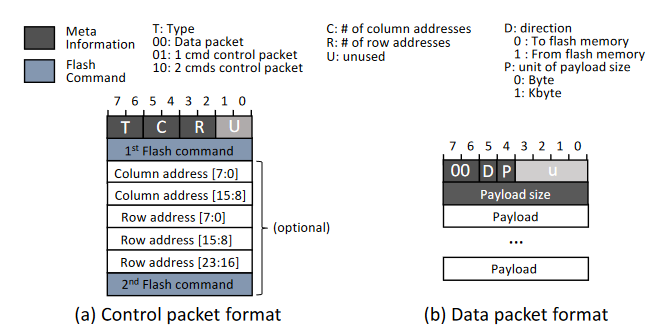

Packet

On-die controller通过packet头的type位来判断包的类型是控制包还是数据包。

- 如果是控制包:包的大小由T,C,R四位来决定,在Flash memory内部生成信号的模式跟在flash controller中生成信号的模式非常相像。

- 如果是数据包:包的大小由第二个字节决定。

- 额外开销:只有包头的部分,大概是两个字节。但是在packet下信道被拓宽为之前的两倍,一次可以发送16bits的数据,开销可以忽略不计。

在packet将带宽拓展为之前的两倍后,考虑以下两种选项:

- 带宽扩展为原有带宽的两倍;(pSSD)

- 带宽与baseline仍然一样,用额外扩展出来的一倍带宽创建网络,提供flash之间的互连。(pnSSD)

Flash之间的互连网络拓扑

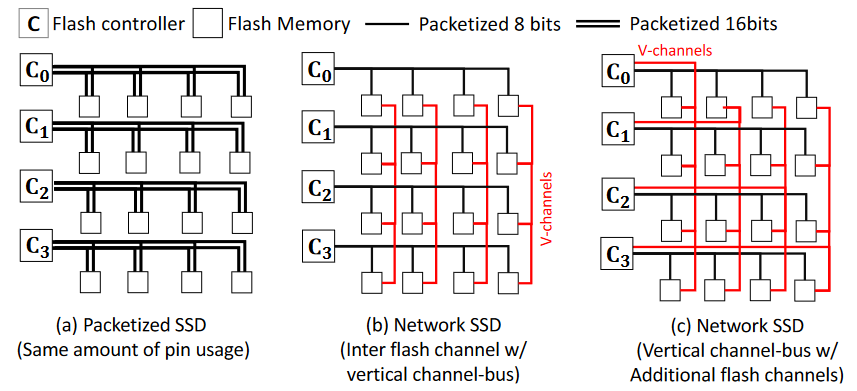

本工作仍然利用现有的总线结构,但是将其扩展到二维,创建2D总线拓扑结构来解决SSD内部网络的问题。

Omnibus网络拓扑

- 除了水平的总线,试图增加垂直总线,将带宽平均分为两份。(图b)

- 挑战:总的带宽恢复为原始状态;垂直总线的使用方式是新的挑战。例如,水平总线的大多数控制来自flash controller,但在(b)中是不可能的,在b的拓扑结构中每个列中的flash之一需要有效地充当每个垂直通道总线的控制器。

- 方案:修改为图(c)的拓扑结构,这利用了在packet化之后,flash控制器引脚带宽能够变为之前的两倍且可用。此时一个flash channel控制器可以控制两条总线,一个水平总线,一个垂直总线。

- 注意:跟以往网络拓扑方案中每个节点既可以做控制也可以做数据交换不同,此网络中控制(flash controller)与数据交换(flash memory)层完全分离

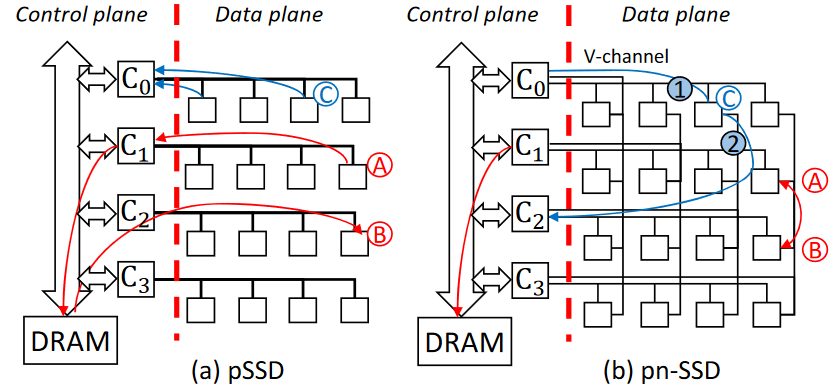

数据平面:路径的多样性

图 展示在flash内部互联上的路径多样性

例1:将A中的数据迁移到B上

例2:将C中的数据读出来

- split选项:可以将一个信息分为两半从两条路径传输过去,同时利用水平和垂直信道。

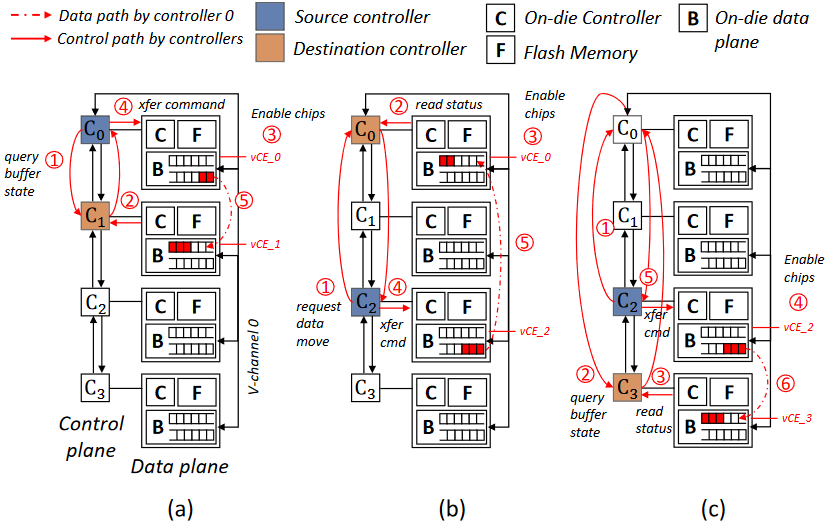

控制平面

图 在flash channel控制器之间的控制平面的作用

当进行一个垂直数据移动时(从源控制器到目标控制器):

例1:C0为源控制器(C0->C1):1-2. 确定on-die plane状态 3. 访问v-channel 0,设置vCE使能信号 4. 发送转移page命令 5. 进行通信

例2:C0为目标控制器(C2->C0):接受到C2的请求后,在on-die plane buffer准备好之后,确保vCE使能信号激活,

例3:C0为中间控制器(C2->C3),在到达C3之前先到达C0

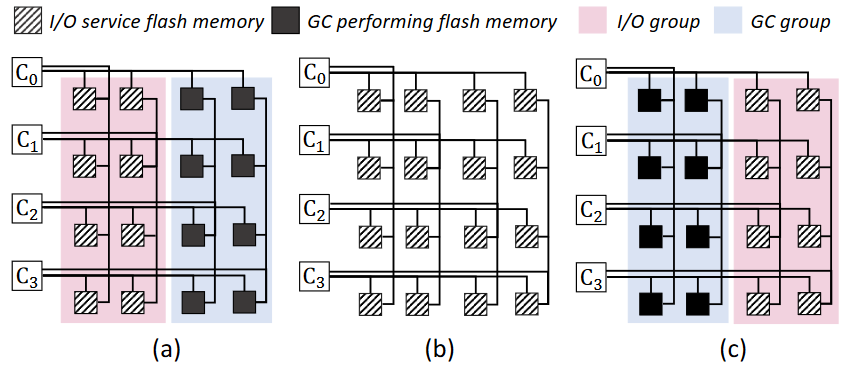

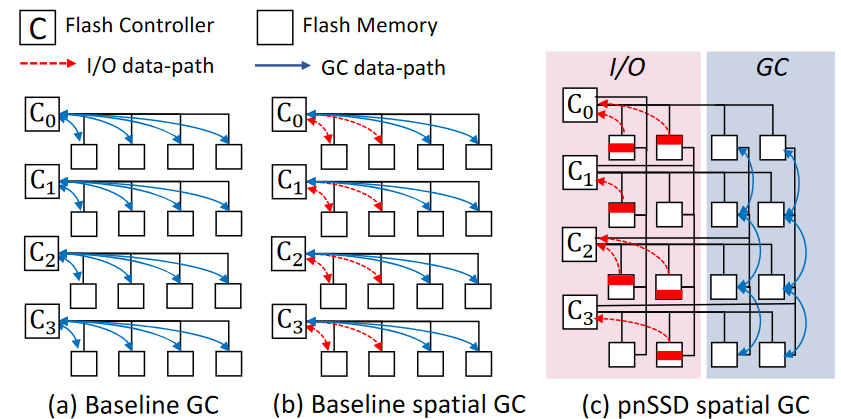

建立互连网络上的垃圾回收机制(Spatial GC机制)

IO与垃圾回收分组

- 将进行IO和进行GC的flash memory分开,使得当I/O组进行I/O服务的时候,GC组不会打扰I/O请求的进行。(b-a-b-c)

- 在有垂直信道的情况下,在GC组可以只通过v-channel进行垃圾回收,不影响水平信道。

- 完全消除了垃圾回收对写操作的影响,但是垃圾回收对读操作的干扰仍然无法避免。一般将GC组设计为四分之一大小。

I/O与垃圾回收同时操作

使用设计的互连网络,这种垃圾回收机制的优势能够更加凸显出来,因为它们占用的是不同的信道。此时I/O与垃圾回收可以同时进行,最小化干扰。

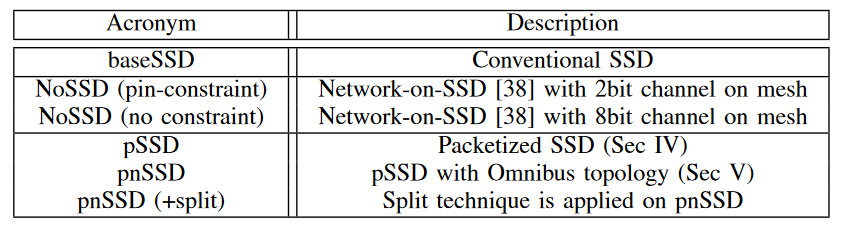

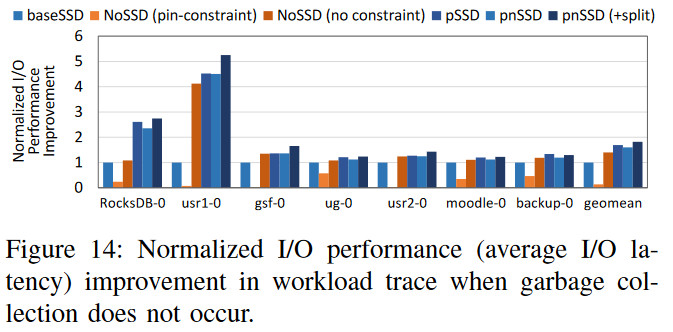

实验结果

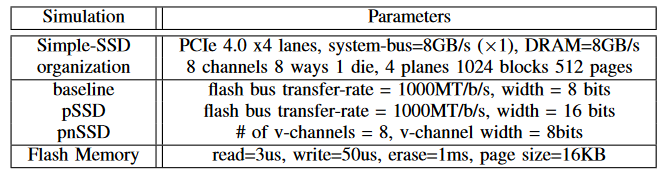

实验配置

SimpleSSD-standalone模拟器

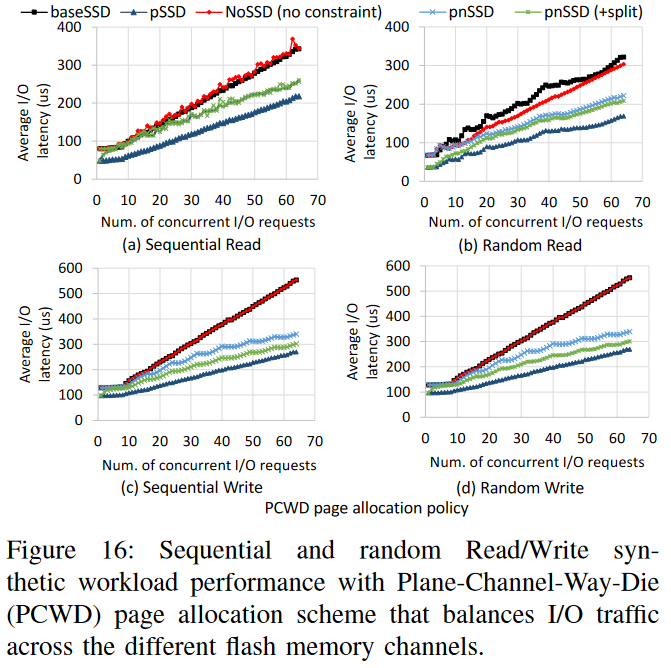

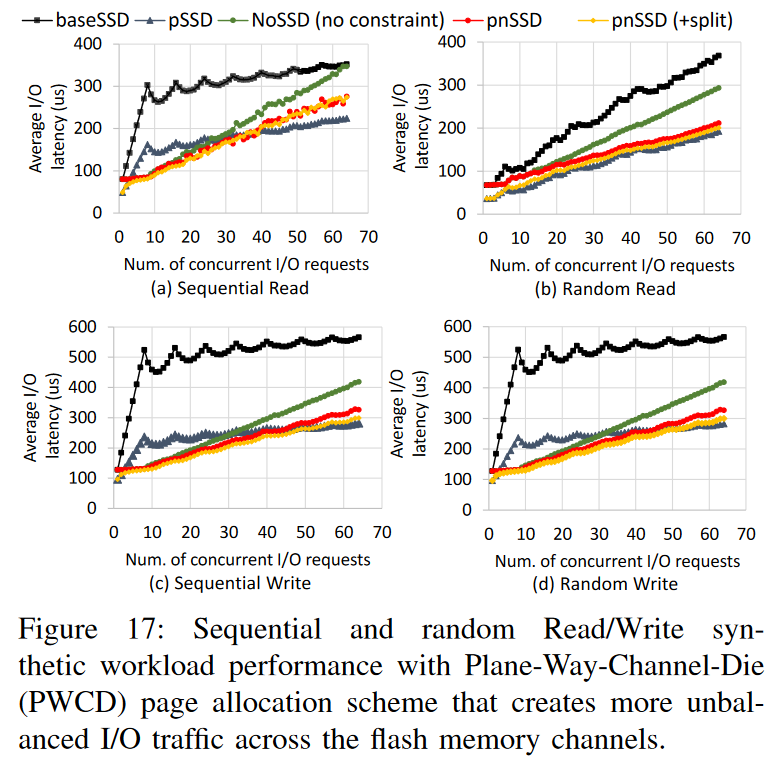

I/O表现

pSSD: 69%, pnSSD: 60%, pnSSD-split:82%

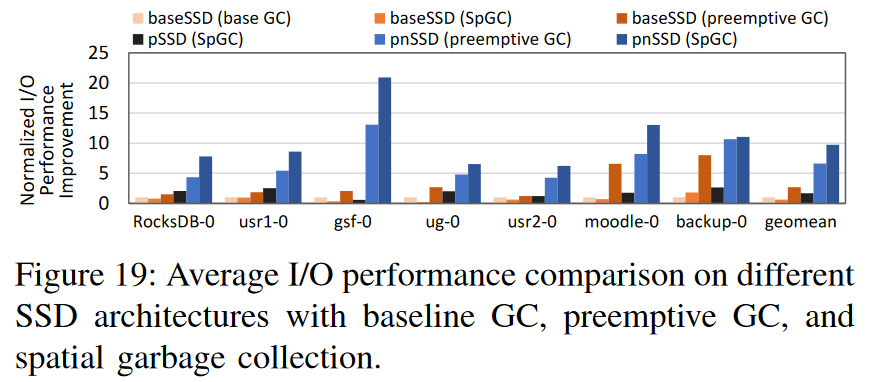

垃圾回收效果

相比于baseline和pSSD,pnSSD平均提升性能9.7X、 5.9X

- 本文作者: Zhang Xinmiao

- 本文链接: https://recoderchris.github.io/2022/12/02/networked-SSD/

- 版权声明: 本博客所有文章除特别声明外,均采用 MIT 许可协议。转载请注明出处!